16-04-2025, 01:02 PM

Hi All.

Time for another update.

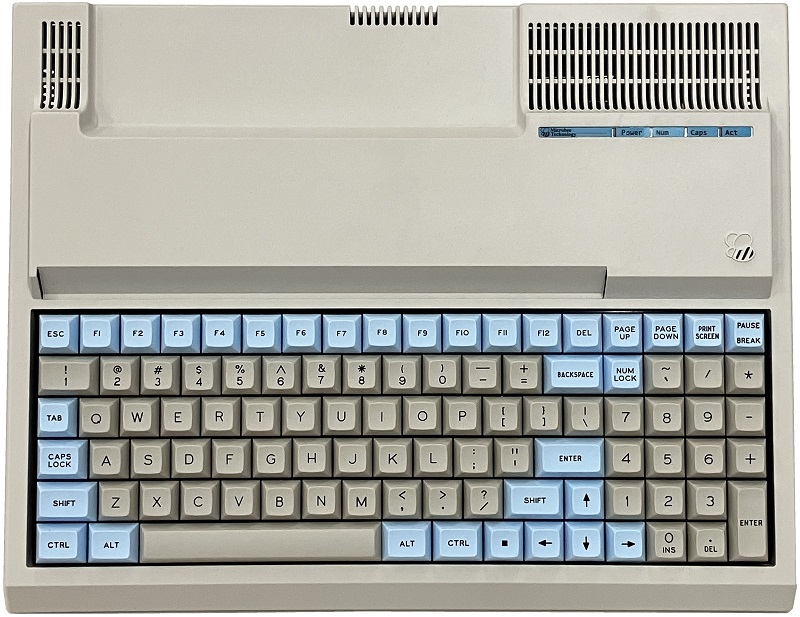

Firstly, the first batch of the production key caps for the 98 key model are finally in.

As you will see from the photo, the colours have changed to better align with the ABS case.

They are a little darker than the case on purpose, and the blue keys have been toned down a little.

Much happier with the look compared to the prototype set that had white keys.

The white was too stark for the beige case.

Hopefully you'll agree.

The last few weeks have been spent on getting the Z80 to work at 20Mhz rather than the 10Mhz of the initial spec.

I didn't consider 20Mhz initially as the Z80PIO was only ever made as a maximum 10Mhz part (Z84C2010PEC/G),

however, the Z80CPU was made to a max frequency of 20Mhz (Z84C0020PEC/G).

I really wanted to be able to run the Z80 at 20Mhz because the new 4 bit-plane graphics modes require a lot more data to be

moved around (4 times the data, + palette information etc.) and I didn't want it to be ' pretty but slow '.

So, I came up with a scheme whereby the PIO could still be clocked at 10Mhz, with some logic in place, while the CPU

was running at 20Mhz.

I had to cater for all accesses to the PIO to have wait states (if the CPU was running at 20Mhz) and

also detection of the interrupt acknowledge cycle (M1 & IORQ active), and also the bus snooping that the PIO does to detect

a return from interrupt instruction that clears it's internal interrupt logic tree.

Aside from the PIO clocking adjustments, the main Z80 system ram and 'Boot ram' have been changed to faster speed parts

along with the HCT245, HCT541 & HCT32 parts changed to AHCT equivalents for smaller propagation delays to meet the 20Mhz

CPU's timing requirements.

Running at 20Mhz came up as expected, but initially it would hang on disk activity. It took me a week of diagnosis to find out that

the emulation code (that the 68SZ328 runs for Floppy disk <-> SDcard handling) needed a tweak.

When the Z80 reads or writes the floppy disk ports the Z80 is immediately held in a BUSREQ/ACK state while the emulation code

on the 68SZ328 figures out what needs handling.

Logic inside the FPGA automatically starts the BUSREQ hold of the Z80 when a FDC port access happens, then this also triggers

an interrupt for the 68SZ328 to handle the emulation processing.

After the processing is done, the 68SZ328 then resets the BUSREQ hold and enables the Z80 to continue running.

The problem was that I was enabling the Z80 to run again before resetting the interrupt register so when the Z80 was running at 20Mhz, it would

fire off another FDC port access before the 68SZ328 was ready for another interrupt, so it would be missed.

This wasn't a problem running at 10Mhz as the 68SZ328's interrupt was reset before another Z80 FDC access was ever made.

At 20Mhz though, the Z80 got in again too quick.

After changing the code around so that the interrupt was cleared before enabling the Z80 to run again all came good.

In all of this work, I also found that the WD2793 disk controller also needed wait states to meet timing even at 10Mhz, so that was

added as well.

Long story short, our new models now run at either 3.375Mhz, 10Mhz, or 20Mhz.

Time for another update.

Firstly, the first batch of the production key caps for the 98 key model are finally in.

As you will see from the photo, the colours have changed to better align with the ABS case.

They are a little darker than the case on purpose, and the blue keys have been toned down a little.

Much happier with the look compared to the prototype set that had white keys.

The white was too stark for the beige case.

Hopefully you'll agree.

The last few weeks have been spent on getting the Z80 to work at 20Mhz rather than the 10Mhz of the initial spec.

I didn't consider 20Mhz initially as the Z80PIO was only ever made as a maximum 10Mhz part (Z84C2010PEC/G),

however, the Z80CPU was made to a max frequency of 20Mhz (Z84C0020PEC/G).

I really wanted to be able to run the Z80 at 20Mhz because the new 4 bit-plane graphics modes require a lot more data to be

moved around (4 times the data, + palette information etc.) and I didn't want it to be ' pretty but slow '.

So, I came up with a scheme whereby the PIO could still be clocked at 10Mhz, with some logic in place, while the CPU

was running at 20Mhz.

I had to cater for all accesses to the PIO to have wait states (if the CPU was running at 20Mhz) and

also detection of the interrupt acknowledge cycle (M1 & IORQ active), and also the bus snooping that the PIO does to detect

a return from interrupt instruction that clears it's internal interrupt logic tree.

Aside from the PIO clocking adjustments, the main Z80 system ram and 'Boot ram' have been changed to faster speed parts

along with the HCT245, HCT541 & HCT32 parts changed to AHCT equivalents for smaller propagation delays to meet the 20Mhz

CPU's timing requirements.

Running at 20Mhz came up as expected, but initially it would hang on disk activity. It took me a week of diagnosis to find out that

the emulation code (that the 68SZ328 runs for Floppy disk <-> SDcard handling) needed a tweak.

When the Z80 reads or writes the floppy disk ports the Z80 is immediately held in a BUSREQ/ACK state while the emulation code

on the 68SZ328 figures out what needs handling.

Logic inside the FPGA automatically starts the BUSREQ hold of the Z80 when a FDC port access happens, then this also triggers

an interrupt for the 68SZ328 to handle the emulation processing.

After the processing is done, the 68SZ328 then resets the BUSREQ hold and enables the Z80 to continue running.

The problem was that I was enabling the Z80 to run again before resetting the interrupt register so when the Z80 was running at 20Mhz, it would

fire off another FDC port access before the 68SZ328 was ready for another interrupt, so it would be missed.

This wasn't a problem running at 10Mhz as the 68SZ328's interrupt was reset before another Z80 FDC access was ever made.

At 20Mhz though, the Z80 got in again too quick.

After changing the code around so that the interrupt was cleared before enabling the Z80 to run again all came good.

In all of this work, I also found that the WD2793 disk controller also needed wait states to meet timing even at 10Mhz, so that was

added as well.

Long story short, our new models now run at either 3.375Mhz, 10Mhz, or 20Mhz.